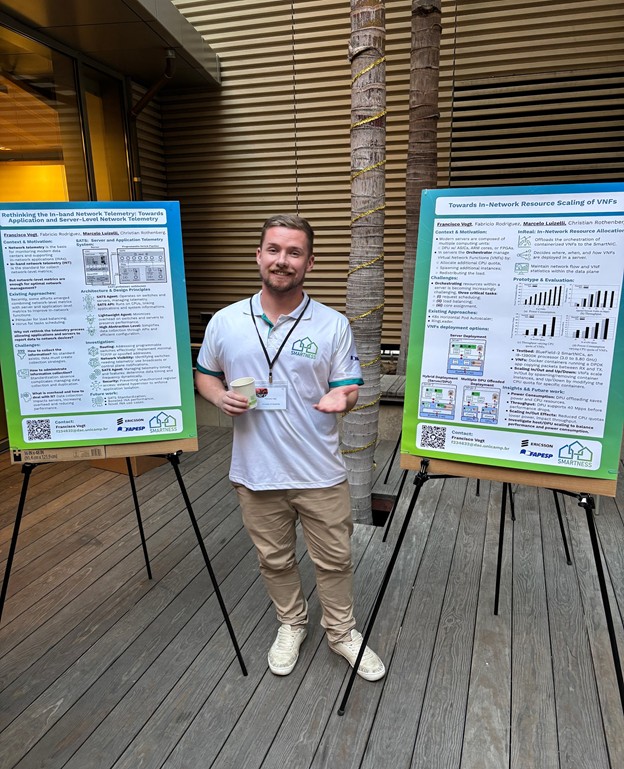

The SMARTNESS team participated in the ACM CoNEXT 2024 conference, held last week in Los Angeles, USA. The team, comprising PhD students Francisco Vogt (UNICAMP), Washington Silva (UFSCar), Guilherme Matos (UFSCar), and Professor Dr. Marcelo Luizelli (UNIPAMPA), presented four works at the event, including contributions to the Student Workshop and poster sessions.

Research Contributions:

– Towards In-Network Resource Scaling of VNFs

Presented by Francisco Vogt and Prof. Dr. Marcelo Luizelli, this poster introduces InReal (In-Network Resource Allocation), a system designed for provisioning and managing containerized Virtual Network Functions (VNFs). InReal optimizes CPU utilization, enhances power efficiency, and ensures that VNF performance requirements are met.

– Rethinking the In-band Network Telemetry: Towards Application and Server-Level Network Telemetry

In this work, Francisco Vogt and Prof. Dr. Marcelo Luizelli proposed an approach to telemetry within programmable networks, wherein applications and servers transmit telemetry data directly to network devices, such as programmable switches and SmartNICs. This methodology enables in-network applications to make informed decisions based on comprehensive server and application contexts.

Washington Silva presented a collaborative inference method aimed at offloading augmented reality tasks, such as object recognition, to heterogeneous edge devices. This paper addresses the computational and energy constraints of mobile devices, facilitated by advancements in 5G technology. This approach reduces latency for users and lowers operational costs for service providers.

Guilherme Matos discussed an evaluation of the performance of disaggregating monolithic applications across heterogeneous hardware. The study demonstrated that disaggregation maintains performance with minimal impact from network latency and improves cache utilization, reducing L1 cache misses and L2 accesses. Future research directions include memory optimization strategies and the integration of GPUs and FPGAs to further improve computational efficiency.